# Oxidized Titanium as a Gate Dielectric for Graphene Field Effect Transistors and Its Tunneling Mechanisms

Chris M. Corbet, Connor McClellan, Kyounghwan Kim, Sushant Sonde, Emanuel Tutuc, and Sanjay K. Banerjee<sup>\*</sup>

Microelectronics Research Center, The University of Texas at Austin, Austin, Texas 78758, United States

**ABSTRACT** We fabricate and characterize a set of dual-gated graphene field effect transistors using a novel physical vapor deposition technique in which titanium is evaporated onto the graphene channel in 10 Å cycles and oxidized in ambient to form a top-gate dielectric. A combination of X-ray photoemission spectroscopy, ellipsometry, and transmission electron microscopy suggests that the titanium is oxidizing *in situ* to titanium dioxide. Electrical characterization of our devices yields a dielectric constant of  $\kappa = 6.9$

with final mobilities above 5500 cm<sup>2</sup>/(V s). Low temperature analysis of the gate-leakage current in the devices gives a potential barrier of 0.78 eV in the conduction band and a trap depth of 45 meV below the conduction band.

**KEYWORDS:** graphene · transistor · dielectric · seed layer · titanium oxide · gate leakage

ver the past decade, great strides have been made in graphene fieldeffect transistors (GFET): wafer scale growth,<sup>1</sup> dual-gated high mobility devices,<sup>2</sup> and large-scale integration<sup>3,4</sup> have been achieved. Of particular note is graphene's utility in analog RF circuits,<sup>5</sup> creating possibilities for ultrahigh frequency electronics.<sup>6</sup> These devices require high mobility and low gate leakage currents, necessitating advancements in high quality GFET gate dielectrics.<sup>5</sup>

While there have been many recent studies of GFETs<sup>1-6</sup> and graphene-dielectricgraphene heterostructures,<sup>7-9</sup> there are still gaps in our understanding of the surface reaction kinetics<sup>10</sup> and conduction mechanisms<sup>11</sup> through graphene gate dielectrics, and many of the physical properties of these gate dielectric materials remain unclear. The guest for novel graphene devices such as graphene tunnel FETs<sup>12,13</sup> will also require a greater understanding of these materials and how they affect the electrical characteristics of graphene devices. The focus of this work is to shed light on a novel physical vapor deposition (PVD) method used to fabricate the GFET top gate stack.

We study the scaling properties of oxidized titanium as a gate dielectric for GFETs. Previous work has shown that oxidized aluminum and oxidized titanium (TiO<sub>x</sub>) can be used as a nucleation site for dielectrics deposited *via* atomic layer deposition.<sup>2,14,15</sup> In this study, we use only cycles of PVD of titanium and subsequent oxidation to form the gate dielectric. We fabricated a set of dual-gated GFETs with different dielectric thicknesses between 2.4 and 12 nm. Furthermore, we analyzed the gate leakage current in GFETs with TiO<sub>x</sub> gate dielectrics as a function of temperature and electric field.

## **RESULTS AND DISCUSSION**

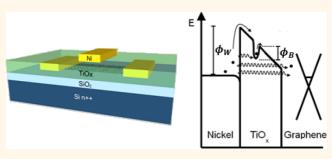

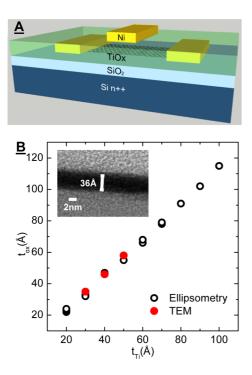

We created a set of dual-gated GFETs to determine the properties of oxidized titanium as a dielectric in graphene devices. Figure 1A shows a schematic of the dualgated GFET. To accurately determine the characteristics of TiO<sub>x</sub> as a dielectric, a precise measurement of the oxide thickness is essential. The dielectric thickness after the cyclic deposition of the TiO<sub>x</sub> (see Materials and Methods) was determined using a combination of ellipsometry and transmission

\* Address correspondence to banerjee@ece.utexas.edu.

Received for review July 14, 2014 and accepted September 26, 2014.

Published online September 26, 2014 10.1021/nn5038509

© 2014 American Chemical Society

VOL. 8 • NO. 10 • 10480-10485 • 2014

Figure 1. (A) Device schematic. (B) Measured  $t_{ox}$  as a function of  $t_{Ti}$  for all devices obtained *via* ellipsometry and TEM. Inset: TEM image of the TiO<sub>x</sub> on the graphene channel.

electron microscopy (TEM). For every fabricated GFET created in this work, a control Ti-on-Si sample was processed in parallel to measure the dielectric thickness by ellipsometry. In addition, cross-sectional TEMs were taken for several graphene devices to determine the thickness of the  $TiO_x$  on the graphene active area as compared to ellipsometry measurements of the silicon substrates. Figure 1B gives the deposited Ti film thickness  $(t_{ox})$  vs the measured oxide thickness  $(t_{ox})$  from ellipsometry and TEM. The inset of Figure 1B shows a cross-sectional TEM of three cycles of  $TiO_x$  on the graphene channel. For every 10 Å of titanium deposited on the bare silicon substrates, 11–12 Å of oxidized titanium is produced. TEM data were obtained for three GFETs with different TiO<sub>x</sub> thicknesses, all showing a dielectric thickness within 3 Å of ellipsometric measurements on the silicon controls.

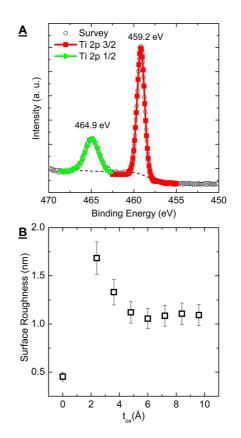

The composition of the TiO<sub>x</sub> was also investigated with X-ray photoemission spectroscopy (XPS) on the Si control substrates. Figure 2A shows the number of electrons vs the binding energy of the electrons collected in the area around the Ti 2p bond states. There are two distinct peaks at 459.2 and 464.9 eV, representing the Ti 2p 3/2 and Ti 2p 1/2 states, commonly associated with titanium dioxide TiO<sub>2</sub>.<sup>16</sup> The peak broadening of the Ti 2p 3/2 state in XPS measurements associated with other forms titanium oxides<sup>17</sup> was not present. Additionally, TiO<sub>2</sub> formed with similar methods has been found to be the rutile phase.<sup>18</sup> The rutile phase of TiO<sub>2</sub> has a bond length of 1.98 Å and bond angles of 81° and 91°, yielding a unit cell *z*-height

Figure 2. (A) XPS spectra of 8.4 nm  $TiO_x$  on a Si control sample. Each of the 2p bonding states shows a single Gaussian peak indicating pure  $TiO_2$ . (B) Measured  $R_s$  as a function of  $t_{ox}$ .

of 2.96 Å.<sup>19</sup> The oxidation of Ti to TiO<sub>2</sub> would cause the as-deposited Ti film to grow, at a minimum, to three times its deposited thickness. However, the deposited film only increases in thickness by ~10% per cycle, suggesting that the evaporating titanium is oxidizing primarily *in situ* rather than in ambient. This finding suggests that the residual oxygen in the e-beam evaporation chamber, combined with the low deposition rate allows for oxidation during the Ti deposition.

Additionally, the surface roughness ( $R_s$ ) as a function of oxide thickness was studied. Figure 2B shows the surface roughness of the graphene channel as a function of  $t_{ox}$ . Graphene channels after annealing had a  $R_s < 0.5$  nm, increasing to ~1.6 nm for the thinnest working  $t_{ox}$  and leveling at ~1.1 nm above 4.8 nm. There was a 10% variation in  $R_s$  for similar thicknesses depending on the device studied.

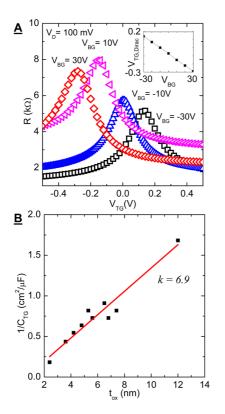

Figure 3A shows a dual-gated GFET channel resistance (*R*) measured as a function of the top gate voltage ( $V_{TG}$ ) at different back-gate voltages ( $V_{BG}$ ) for 4.8 nm TiO<sub>x</sub>. The inset of Figure 3A shows the  $V_{TG}$  value at the charge neutrality point ( $V_{TG,Dirac}$ ) as a function of  $V_{BG}$ .  $V_{TG,Dirac}$  has a linear dependence on  $V_{BG}$ , with a slope equal to the ratio of the back-gate ( $C_{BG}$ ) to top-gate capacitance ( $C_{TG}$ ). The  $C_{BG}$  values are measured using 100  $\times$  100  $\mu$ m<sup>2</sup> metal pads on the SiO<sub>2</sub> back-gate

VOL.8 • NO.10 • 10480-10485 • 2014

JAI

www.acsnano.org

Figure 3. (A) *R* vs V<sub>TG</sub> measured in a dual gated graphene FET at different V<sub>BG</sub>. The 4.8 nm TiO<sub>x</sub> top dielectric was deposited with repeated deposition of titanium and subsequent oxidation. The inset gives V<sub>TG,Dirac</sub> vs V<sub>BG</sub> measured from the *R* vs V<sub>TG</sub> traces. The slope of the line corresponds to C<sub>BG</sub>/C<sub>TG</sub>. (B) C<sup>-1</sup><sub>TG</sub> vs t<sub>ox</sub> for dual-gated graphene FETs with TiO<sub>x</sub> dielectrics. The *k*-value of TiO<sub>x</sub> is 6.9 represented by the slope of the fitted line.

dielectric in close proximity of the GFET, and are independently measured with values of 8–13 nF/cm<sup>2</sup>. Using these values of  $C_{BG}$  and the ratio of  $C_{BG}/C_{TG}$ , the  $C_{TG}$  value is calculated for each dual-gated GFET. Figure 3B shows the inverse of the capacitance per unit area ( $C^{-1}_{TG}$ ) vs the physical thickness of the TiO<sub>x</sub>. The data are extracted from over ten devices with various thicknesses.  $C_{TG}^{-1}$  has a linear dependence on  $t_{ox}$  the slope indicating a TiO<sub>x</sub>  $\kappa$ -value of 6.9. The y-value intercept of the  $C_{TG}^{-1}$  vs  $t_{ox}$  dependence is zero, within experimental error.

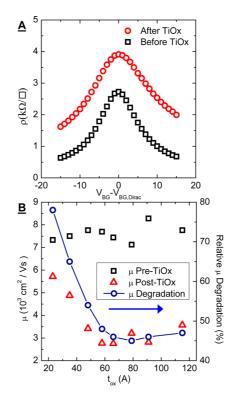

Figure 4A shows the resistivity ( $\rho$ ) as a function of  $V_{BG}$ , centered around the charge neutrality point ( $V_{BG,Dirac}$ ) for a device before and after 2.4 nm of TiO<sub>x</sub> was deposited on the channel. The device mobility ( $\mu$ ), extracted using the model of Kim *et al.*,<sup>2</sup> is 7300 cm<sup>2</sup>/(V s) before deposition, and 5700 cm<sup>2</sup>/(V s) after the TiO<sub>x</sub> was deposited. All devices showed a ~25% increase in mobility at 77 K, consistent with previous reports.<sup>14</sup> Figure 4B gives  $\mu$  before and after TiO<sub>x</sub> deposition for all values of  $t_{ox}$ . The initial  $\mu$  value degrades after TiO<sub>x</sub> deposition for all values of  $t_{ox}$ . The line connecting the points between different  $t_{ox}$  values represents the relative  $\mu$  degradation of each device as a function of  $t_{ox}$ . Devices with similar starting  $\mu$  are chosen to help

Figure 4. (A)  $\rho vs V_{BG} - V_{BG,Dirac}$  before and after deposition of 2.4 nm of TiO<sub>x</sub>. The mobility was 7400 and 5800 cm<sup>2</sup>/(V s) before and after deposition, respectively. (B)  $\mu vs t_{ox}$  for devices with varying TiO<sub>x</sub> gate dielectric thicknesses. Data points that are vertically aligned represent a single device, *i.e.*, mobility of FETs indicated by squares degrade to those indicated by triangles after Ti deposition. The blue line (right axis) represents the relative degradation of the devices.

clarify the effects of dielectric deposition on the electrical characteristics of the GFETs. The initial  $\mu$  degradation is rapid at small  $t_{\rm ox}$  values, but levels off, at ~50% of the initial starting value for  $t_{\rm ox} > 50$  Å. These measurements are similar to previous studies of the graphene channel mobility dependence on dielectric thickness where mobility degradation was attributed to scattering from oxygen vacancies in the dielectric layer.<sup>14,15</sup> Additionally, oxygen vacancies in TiO<sub>2</sub> are known to be prevalent and could form filaments and parallel conduction pathways when biased appropriately as with resistive switching RAM.<sup>20–22</sup> Further studies in mobility degradation mechanisms in topgated GFETs will be the attention of future work.

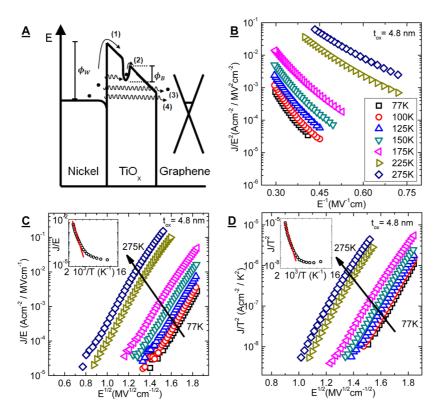

The gate leakage current density (*J*) from the graphene channel to the top gate electrode through the TiO<sub>x</sub> was measured, and the data compared with different models to try to elucidate dominant leakage mechanisms. We indicate possible gate dielectric conduction mechanisms in our GFETs in Figure 5A, with the corresponding equations shown below. Four mechanisms might determine the leakage through the gate dielectric. The first is thermionic emission,<sup>23</sup> in which carriers are thermally excited over the tunnel barrier at the electrode-dielectric interface. The

VOL. 8 • NO. 10 • 10480-10485 • 2014

Figure 5. (A) Energy band diagram schematically showing (1) thermionic emission, (2) Poole-Frenkel tunneling, (3) Fowler-Nordheim tunneling, and (4) direct tunneling. Solid arrows represent a thermal excitation, while wavy lines represent a tunneling process. Diagram is not to scale. (B) Fowler-Nordheim plot showing  $J/E^2$  vs  $E^{-1}$ . Decreasing slopes at higher temperatures may be indicative of thermally activated processes. Relatively low negative slope at low fields (right) may be indicative of trap-assisted tunneling processes. (C) Thermionic emission plot showing  $J/T^2$  vs  $E^{1/2}$ . Inset shows  $J/T^2$  vs 1000/T at constant E = 1.85 MV/cm. Red line intercept gives  $\phi_B = 42$  meV. (D) Poole-Frenkel plot showing J/E vs  $E^{1/2}$ . Inset shows J/E vs 1000/T at units for the insets of (C) and (D) are the same as the parent figure.

thermionic current density  $(J_{TH})$  has the following dependence on temperature (*T*), and electric field (*E*):

$$J_{\rm TH} \propto T^2 \cdot \exp\left[\frac{-q}{k_{\rm B}T}\left(\varphi_{\rm W} - \sqrt{\frac{qE}{4\pi\varepsilon}}\right)\right]$$

(1)

where *q* is the electron charge,  $k_{\rm B}$  is the Boltzmann constant,  $\phi_{\rm W}$  is barrier height between the metal and the TiO<sub>x</sub>, and  $\varepsilon$  is the dynamic permittivity. The second mechanism is Poole-Frenkel<sup>23</sup> in which electrons tunnel into dielectric trap states, and then are thermally excited into the channel. In this scenario, the current density ( $J_{\rm PF}$ ) depends on *E* and *T* as follows:

$$J_{\rm PF} \propto E \cdot \exp\left[\frac{-q}{k_{\rm B}T}\left(\varphi_{\rm B} - \sqrt{\frac{qE}{4\pi\varepsilon}}\right)\right]$$

(2)

where  $\phi_{\rm B}$  is the trap depth. The current density ( $J_{\rm FN}$ ) resulting from tunneling through the triangular potential barrier<sup>21</sup> (Fowler-Nordheim tunneling) has the following dependence on *E*:

$$J_{\rm FN} \propto E^2 \cdot \exp\left(\frac{-4}{3} \frac{\sqrt{2qm_{\rm ox}}}{\hbar} \frac{\varphi_{\rm W}^{3/2}}{E}\right)$$

(3)

where  $m_{ox}$  is the mass of the carrier in the dielectric and  $\hbar$  is Planck constant. Finally, the current density ( $J_{DT}$ )

resulting from direct tunneling through the potential barrier<sup>23</sup> has the following dependence on E:

$$J_{\rm DT} \propto \frac{E^2}{\varphi_{\rm W}\beta_1} \exp\left(-\frac{2\beta_2\sqrt{2qm_{\rm ox}}}{\hbar}\frac{\varphi_{\rm W}^{3/2}}{E}\right) \qquad (4)$$

where  $J_{\text{DT}}$  is the direct tunneling current density,  $\beta_1$  and  $\beta_2$  are unit-less correction terms depending on  $\phi_W$  and E, and  $m_{\text{ox}}$  is the effect mass of the carrier.  $\phi_W$  is determined by the difference in the nickel Fermi energy ( $E_{\text{F,Ni}}$ ) and the electron affinity of the TiO<sub>2</sub> ( $\chi_{\text{TiO2}}$ ). Given that  $E_{\text{F,Ni}}$  is 4.6 eV and  $X_{\text{TiO2}}$  is 3.9 eV,<sup>24</sup> we expect  $\phi_W$  to be approximately 0.5 eV.

The *J* values were experimentally determined by biasing the graphene layer at 0.1 V between the source and drain electrodes, and varying the top-gate electrode bias from -1.5 to 1.5 V, while keeping  $V_{BG}$  at 0 V. To assess the Fowler-Nordheim and direct tunneling mechanisms in Figure 5B, we plot  $J/E^2$  as a function of  $E^{-1}$  on a semi-log plot at multiple temperatures. In devices with low dielectric thickness, Fowler-Nordheim tunneling is characterized by a temperature independent negative slope at high *E*, while direct tunneling is indicated by a temperature independent positive slope at low  $E.^{23,25}$  In our devices, we find strong temperature dependence for T > 125 K, indicating

VOL. 8 • NO. 10 • 10480-10485 • 2014

thermally activated processes occurring at elevated temperatures. The positive slope of  $J/E^2$  at low *E* expected for direct tunneling was not seen in any of our devices. Instead, we observed a slow decrease in slope with decreasing field consistent with trapassisted tunneling.<sup>26</sup>

At high fields and low temperatures, the data is consistent with Fowler-Nordheim tunneling. Using eq 3 and the high-field slope of  $\ln(J/E^2)$  vs  $E^{-1}$  at 77 K, we experimentally determine  $\phi_W = 1.0$  eV. We assumed the tunneling effective mass in TiO<sub>2</sub> to be the electron rest mass. However, we note that the effective mass in TiO<sub>2</sub> has been reported to range between 0.7 and 14 m<sub>0</sub>.<sup>27</sup>

To probe the role of the thermionic emission, in Figure 5C we show  $J/T^2$  vs  $E^{1/2}$  on a semi-log plot at various temperatures. Figure 5C inset is a semi-log Arrhenius plot of  $J/T^2$  at a fixed E = 2 MV/cm. In the parent figure, thermionic emission is characterized by a linear slope of the  $J/T^2$  on  $E^{1/2}$ . In the inset, this conduction mechanism is shown by the magnitude of  $J/T^2$  being linearly dependent on  $T^{-1}$  at a constant *E*. In these devices, we find the slope of  $J/T^2$  to be linear with respect to  $E^{1/2}$ . At constant *E*, there is a nearly linear dependence of  $J/T^2$  at T > 150 K with a weak or no dependence at lower temperatures. Using eq 2, we are able to experimentally determine  $\phi_W$  from the y-intercept of the linear Arrhenius dependence of  $J/T^2$  at constant *E* and *T* > 150 K. In this temperature regime,  $\phi_W$  was 0.75–0.80 eV when calculated from E = 1.9-2.1 MV/cm. The discrepancy between the  $\phi_W$  found in the low temperature  $J_{\text{FN}}$  regime and the high temperature  $J_{\text{TH}}$ can be attributed to the uncertainty in the effective mass.

To analyze Poole-Frenkel mechanism, in Figure 5D we plot J/E vs  $E^{1/2}$  at various temperatures. The inset gives a semi-log Arrhenius plot of J/E at constant E = 1.85 MV/cm. The main panel data shows a linear

In(*J*/*E*) vs  $E^{1/2}$  dependence, consistent with Poole-Frenkel tunneling. Figure 5D shows that the magnitude of *J*/*E* has an exponential dependence on  $T^{-1}$ , at constant *E*. Using eq 2, we extract  $\phi_{\rm B}$  to be 30–70 meV for E = 1.75 - 1.9 MV/cm. Trap depths in polycrystalline TiO<sub>x</sub> films have been found ranging between 30 meV and 0.9 eV depending on the preparation method and oxidation structure of the TiO<sub>x</sub>.<sup>28,29</sup>

These findings suggest that the gate leakage is controlled by a combination of all of these mechanisms dependent on the field and temperature of the device. At temperatures below 125 K and high *E* fields, *J* is dominated by Fowler-Nordheim tunneling through the triangular potential barrier. At similar temperatures and low *E* fields, trap assisted tunneling occurs in which the carriers find trap states in the dielectric before tunneling through the rest of the barrier. For all *E* and temperatures above 150 K, *J* is a combination of Poole-Frenkel tunneling and thermionic emission in which thermal excitation enhances the leakage current.

## CONCLUSION

In summary, repeated cycles of PVD and oxidation of titanium was able to achieve high performance GFETs. We find that the Ti PVD layer is primarily oxidized *in situ* to TiO<sub>2</sub>. By measuring a set of devices with different  $t_{ox}$ , we determine the dielectric constant of oxidized titanium to be  $\kappa = 6.9$ . Finally, we measured the leakage currents and investigated the possible conduction mechanisms in TiO<sub>x</sub> gate dielectrics. While it is difficult to make definitive conclusions, we found evidence of Fowler-Nordheim tunneling at temperatures below 125 K and a combination of Poole-Frenkel tunneling and thermionic emission at temperatures above 125 K. This analysis suggests a conduction band edge barrier height of 0.78 eV and a trap depth of ~45 meV below the conduction band.

#### MATERIALS AND METHODS

**Dielectric Materials and Deposition.** Titanium pellets better than 99.99% pure were placed in a titanium carbide crucible, both obtained from Kurt J. Lesker corporation. Films were deposited using an SEC-600 e-beam evaporator from CHA Industries. Films with a thickness of 10 Å were electron beam evaporated at a rate of less than 0.1 Å/s, at a starting pressure of  $5 \times 10^{-6}$  Torr background pressure, and then vented to atmosphere. During deposition, the pressure of the system drops to  $\sim 1 \times 10^{-6}$  Torr and the exposure to atmosphere was less than 1 min when vented between repeated cycles; the maximum deposition temperature was 25 °C. *In situ* thickness measurements were obtained from a quartz crystal monitor.

**Dielectric Thickness Characterization.** Ellipsometry measurements were taken using a JJ Woollam M-2000 ellipsometer. Transmission electron micrographs were obtained with the FEI TECNAI G2 F20 X-TWIN system.

**Transistor Fabrication.** We mechanically exfoliated monolayer graphene layers on 285 nm thermally oxidized SiO<sub>2</sub> grown on highly doped n-type silicon.<sup>30</sup> Graphene monolayers are

identified with a combination of Raman spectroscopy,<sup>31</sup> and optical contrast under white light.<sup>32</sup> We created the back-gated GFET channels with a combination of electron beam lithography (EBL) and oxygen plasma etching. After a subsequent EBL step to define contact regions, nickel was evaporated to form the source and drain. The GFETs were then annealed at 255 °C for 3 h at 9  $\times$  10<sup>-9</sup> Torr to remove process residues while preventing mobility degradation. We surmise the graphene comes into closer contact with the corrugated SiO<sub>2</sub> surface if annealed at temperatures higher than 275 °C, resulting in lower mobilities.<sup>33</sup> A set of GFETs were created using 2–10 cycles of Ti deposition and oxidation. A top gate was then defined by a subsequent EBL step and a nickel top gate electrode was deposited with electron beam evaporation and lift-off. For devices with thicker dielectrics, isolated contact windows were opened using a combination of EBL and CH<sub>4</sub> plasma.

**Electrical Characterization.** All electrical measurements were taken in a Lake Shore Cryotronics cryogenic probe station. All samples were measured in vacuum below  $5 \times 10^{-5}$  Torr and cooled with liquid nitrogen to achieve 77 K where stated. Data

was taken with an Agilent 4156C Semiconductor Parameter Analyzer.

Conflict of Interest: The authors declare no competing financial interest.

Acknowledgment. This was supported in part by the NRI South West Academy of Nanoelectronics and the NSF NNIN program. C. M. Corbet also graciously recognizes funding from the Robert Noyce Memorial Fellowship and the Cockrell School of Engineering Fellowship.

#### **REFERENCES AND NOTES**

- Lee, J.-H.; Lee, E. K.; Joo, W.-J.; Jang, Y.; Kim, B.-S.; Lim, J. Y.; Choi, S.-H.; Ahn, S. J.; Ahn, J. R.; Park, M.-H.; *et al.* Wafer-Scale Growth of Single-Crystal Monolayer Graphene on Reusable Hydrogen-Terminated Germanium. *Science* **2014**, *344*, 286–289.

- Kim, S.; Nah, J.; Jo, I.; Shahrjerdi, D.; Colombo, L.; Yao, Z.; Tutuc, E.; Banerjee, S. K. Realization of a High Mobility Dual-Gated Graphene Field-Effect Transistor with Al<sub>2</sub>O<sub>3</sub> Dielectric. *Appl. Phys. Lett.* **2009**, *94*, 062107.

- Kim, K.; Choi, J.-Y.; Kim, T.; Cho, S.-H.; Chung, H.-J. A Role for Graphene in Silicon-Based Semiconductor Devices. *Nature* 2011, 479, 338–344.

- Lin, Y.-M.; Valdes-Garcia, A.; Han, S.-J.; Farmer, D. B.; Meric, I.; Sun, Y.; Wu, Y.; Dimitrakopoulos, C.; Grill, A.; Avouris, P.; et al. Wafer-Scale Graphene Integrated Circuit. Science 2011, 332, 1294–1297.

- Schwierz, F. Graphene Transistors. Nat. Nanotechnol. 2010, 5, 487–496.

- Lin, Y.; Dimitrakopoulos, C.; Jenkins, K. A.; Farmer, D. B.; Chiu, H.; Grill, A.; Avouris, P. 100-GHz Transistors from Wafer-Scale Epitaxial Graphene. *Science* **2010**, *327*, 662.

- Britnell, L.; Gorbachev, R. V.; Jalil, R.; Belle, B. D.; Schedin, F.; Mishchenko, a; Georgiou, T.; Katsnelson, M. I.; Eaves, L.; Morozov, S. V.; *et al.* Field-Effect Tunneling Transistor Based on Vertical Graphene Heterostructures. *Science* 2012, 335, 947–950.

- Britnell, L.; Gorbachev, R. V.; Geim, A. K.; Ponomarenko, L. A.; Mishchenko, A.; Greenaway, M. T.; Fromhold, T. M.; Novoselov, K. S.; Eaves, L. Resonant Tunnelling and Negative Differential Conductance in Graphene Transistors. *Nat. Commun.* **2013**, *4*, 1794.

- 9. Roy, T.; Hesabi, Z. R.; Joiner, C. a.; Fujimoto, a.; Vogel, E. M. Barrier Engineering for Double Layer CVD Graphene Tunnel FETs. *Microelectron. Eng.* **2013**, *109*, 117–119.

- McDonnell, S.; Azcatl, A.; Mordi, G.; Floresca, C.; Pirkle, A.; Colombo, L.; Kim, J.; Kim, M.; Wallace, R. M. Scaling of HfO<sub>2</sub> Dielectric on CVD Graphene. *Appl. Surf. Sci.* **2014**, *294*, 95–99.

- Deen, D. a.; Champlain, J. G.; Koester, S. J. Multilayer HfO<sub>2</sub>/ TiO<sub>2</sub> Gate Dielectric Engineering of Graphene Field Effect Transistors. *Appl. Phys. Lett.* **2013**, *103*, 073504.

- Banerjee, S. K.; Register, L. F.; Member, S.; Tutuc, E.; Reddy, D.; Macdonald, A. H. Bilayer PseudoSpin Field-Elect Transistor (BiSFET): A Proposed New Logic Device. 2009, 30, 158–160.

- Mehr, W.; Dabrowski, J.; Scheytt, J. C.; Lippert, G.; Xie, Y.; Member, S.; Lemme, M. C.; Ostling, M.; Lupina, G. Vertical Graphene Base Transistor. *IEEE Electron Device Lett.* **2012**, *33*, 691–693.

- Fallahazad, B.; Kim, S.; Colombo, L.; Tutuc, E. Dielectric Thickness Dependence of Carrier Mobility in Graphene with HfO<sub>2</sub> Top Dielectric. *Appl. Phys. Lett.* **2010**, *97*, 123105.

- Fallahazad, B.; Lee, K.; Lian, G.; Kim, S.; Corbet, C. M.; Ferrer, D. a.; Colombo, L.; Tutuc, E. Scaling of Al<sub>2</sub>O<sub>3</sub> Dielectric for Graphene Field-Effect Transistors. *Appl. Phys. Lett.* **2012**, *100*, 093112.

- Ekström, H.; Wickman, B.; Gustavsson, M.; Hanarp, P.; Eurenius, L.; Olsson, E.; Lindbergh, G. Nanometer-Thick Films of Titanium Oxide Acting as Electrolyte in the Polymer Electrolyte Fuel Cell. *Electrochim. Acta* 2007, *52*, 4239–4245.

- Kuscer, D.; Kovač, J.; Kosec, M.; Andriesen, R. The Effect of the Valence State of Titanium lons on the Hydrophilicity of Ceramics in the Titanium–Oxygen System. J. Eur. Ceram. Soc. 2008, 28, 577–584.

- Diebold, U.; Li, S.-C.; Schmid, M. Oxide Surface Science. Annu. Rev. Phys. Chem. 2010, 61, 129–148.

- Baur, W. H. Uber Die Verfeinerung Der Kristallstrukturbestimmung Einiger Vertreter Des Rutiltyps: TiO<sub>2</sub>, SnO<sub>2</sub>, GeO<sub>2</sub> Und MgF<sub>2</sub>. Acta Crystallogr. **1956**, *9*, 515–520.

- Park, S.; Magyari-köpe, B.; Nishi, Y. Impact of Oxygen Vacancy Ordering on the Formation of a Conductive Filament in TiO2 for Resistive Switching Memory. *IEEE Electron Device Lett.* **2011**, *32*, 197–199.

- Kwon, D.-H.; Kim, K. M.; Jang, J. H.; Jeon, J. M.; Lee, M. H.; Kim, G. H.; Li, X.-S.; Park, G.-S.; Lee, B.; Han, S.; *et al.* Atomic Structure of Conducting Nanofilaments in TiO<sub>2</sub> Resistive Switching Memory. *Nat. Nanotechnol.* **2010**, *5*, 148–153.

- Hu, C.; McDaniel, M. D.; Posadas, A.; Demkov, A. A.; Ekerdt, J. G.; Yu, E. T. Highly Controllable and Stable Quantized Conductance and Resistive Switching Mechanism in Single-Crystal TiO<sub>2</sub> Resistive Memory on Silicon. *Nano Lett.* 2014, 14, 4360–4367.

- Taur, Y.; Ning, T. H. Fundamentals of Modern VLSI Devices; Cambridge University Press: Cambridge U.K., 2002; Vol. 25, pp 731–733.

- 24. Wu, H.; Wang, L. Electronic Structure of Titanium Oxide Clusters:  $TiO_y$  (y = 1-3) and  $(TiO_2)_n$  (n = 1-4. J. Chem Phys. **1997**, *107*, 8221–8228.

- Register, L. F.; Rosenbaum, E.; Yang, K. Analytic Model for Direct Tunneling Current in Polycrystalline Silicon-Gate Metal–Oxide–Semiconductor Devices. *Appl. Phys. Lett.* 1999, 74, 457.

- Dueñas, S.; Castán, H.; García, H.; Andrés, E. S.; Toledano-Luque, M.; Mártil, I.; González-Díaz, G.; Kukli, K.; Uustare, T.; Aarik, J. A Comparative Study of the Electrical Properties of TiO<sub>2</sub> Films Grown by High-Pressure Reactive Sputtering and Atomic Layer Deposition. *Semicond. Sci. Technol.* 2005, 20, 1044–1051.

- 27. Mardare, D. On the Structure Morphology and Electrical Conductivities of Titanium Oxide Thin Films. *Surf. Sci.* **2002**, *507–510*, 468–472.

- Yildiz, a.; Lisesivdin, S. B.; Kasap, M.; Mardare, D. Electrical Properties of TiO<sub>2</sub> Thin Films. *J. Non. Cryst. Solids* 2008, 354, 4944–4947.

- Mardare, D.; Rusu, G. I. Electrical Conduction Mechanism in Polycrystalline Titanium Oxide Thin Films. J. Non-Cryst. Solids 2010, 356, 1395–1399.

- Novoselov, K. S.; Geim, a K.; Morozov, S. V.; Jiang, D.; Zhang, Y.; Dubonos, S. V.; Grigorieva, I. V.; Firsov, A. A. Electric Field Effect in Atomically Thin Carbon Films. *Science* 2004, *306*, 666–669.

- Ferrari, A. C. Raman Spectroscopy of Graphene and Graphite: Disorder, Electron–Phonon Coupling, Doping and Nonadiabatic Effects. *Solid State Commun.* 2007, 143, 47–57.

- Blake, P.; Hill, E. W.; Castro Neto, A. H.; Novoselov, K. S.; Jiang, D.; Yang, R.; Booth, T. J.; Geim, A. K. Making Graphene Visible. *Appl. Phys. Lett.* **2007**, *91*, 063124.

- Annealing, T.; Sio, W. T.; Cheng, Z.; Zhou, Q.; Wang, C.; Li, Q.; Wang, C.; Fang, Y. Toward Intrinsic Graphene Surfaces: A Systematic Study on Thermal Annealing and Wet-Chemical Treatment of SiO<sub>2</sub>-Supported Graphene Devices. *Nano Lett.* 2011, *11*, 767–771.